RS спусък Принципът на действие на RS-тригера. схема

RS-тригерът е проста контролна машина, обикновено реализирана под формата на цифрова електронна схема, принадлежаща към класа на последователните вериги. Както е известно, в цифровите схеми функционалните устройства от последователен тип включват регистри, броячи, генератори на числа и контролни автомати, включително тригери от различни видове.

Поставете тригерите в цифровата верига

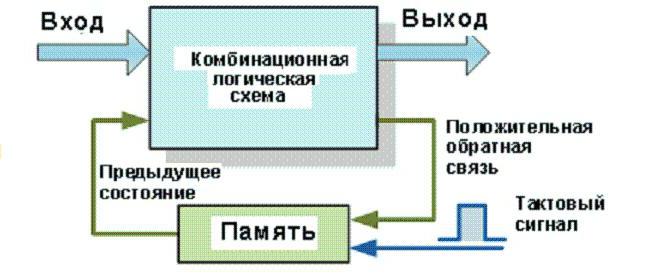

За разлика от комбинационни логически схеми, които променят състоянието в зависимост от действителните сигнали, приложени към техните входове в даден момент, последователната логика има някаква форма на присъща вградена „памет“, така че те могат да вземат предвид както предишното, така и действителното състояние на техните входове. и излиза. Общата блокова схема на последователното устройство е показана по-долу.

RS-тригерът като цифров управляващ автомат включва действителната памет и комбинационната контролна схема на типичните езикови елементи, които реализират своя входен логически алгоритъм. Ако разгледаме тази схема като приложена към най-простите тригерни вериги, тогава те нямат структурирана памет под формата на някаква специализирана микросхема или верижен възел. Паметта на тригера съществува на ниво функция, сякаш е вградена в алгоритъма на неговата комбинаторна схема за контрол. Проявлението на тази "памет" е така наречената бистабилност на спусъка, чиито изходи могат да бъдат в едно от двете основни състояния: логическа единица (по-нататък - 1) или логическа нула (по-нататък - 0). Тригерът запаметява стационарните стойности на своите изходи ("щраква") и записва, докато настъпи следващата промяна на входните сигнали.

класификация

Ако стандартните логически елементи са градивни елементи на комбинационни схеми, бистабилните схеми, включително RS flip-flop, са основните компоненти за изграждане на последователни логически устройства, като регистрите за съхранение на данни, регистрите за смяна, устройствата за памет или броячите. Във всеки случай, разглежданите тригери (разбира се, като всички последователни вериги) могат да бъдат направени от следните основни типове:

1. Асинхронен RS-тригер - верига, която се променя веднага, когато входните сигнали се променят. За типа на въпросните устройства това са сигналите на информационните входове R (нулиране) и S (инсталация). Съгласно установената практика, съответните входове се наричат същите като сигналите върху тях.

2. Синхронен RS-тригер, управляван статично , чиято работа е синхронизирана с нивото на даден часовник.

3. Спусъкът съгласно претенция 2 с динамично управление , който е синхронизиран с моментите на поява на фронтовете (или разпадания) на тактовия сигнал.

Така, ако промените в състоянието на изходите възникнат само в присъствието на тактов сигнал, който се подава към отделен часовник C, тогава спусъкът е синхронен. В противен случай веригата се счита за асинхронна. За поддържане на текущото си състояние последователните вериги използват обратна връзка, т.е. прехвърлят част от изходния сигнал към своя вход.

RS-тригер на логически елементи

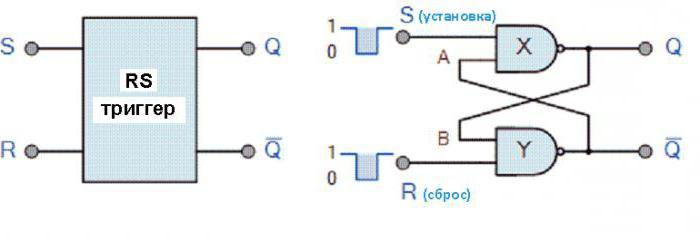

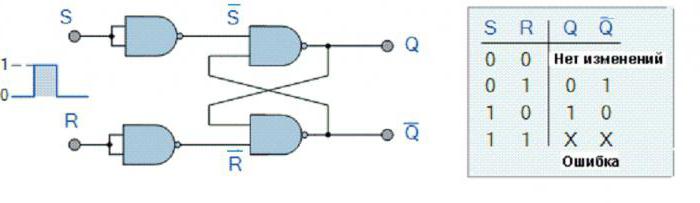

Най-простият начин да се направи това е да се обединят две двойки входни NAND логически елементи. В този случай обратната връзка от изхода на един елемент се подава на входа на друг (вж. Диаграмата по-долу).

Като правило в тази схема входните сигнали се показват като обратни (с долна черта), въпреки че по-късно при анализа на работата се използва нотацията на директните (неинвертирани) входове. Това прави много трудно да се разбере логиката на спусъка. Следователно няма да въвеждаме инверсия на входовете на етапа на разглеждане на действието на веригата върху елементите на NAND, но ще вземем това предвид при модифицирането му.

Колко входа и изхода има RS спусъка? От диаграмата по-горе може да се види, че той съдържа S-вход и R-вход, които служат съответно за настройка и нулиране на веригата, както и за директни Q и обратни Q̃ изходи. Но този най-прост тригер се отнася до асинхронния тип, неговият символ е показан по-долу.

В синхронното устройство има и вход С за тактови импулси.

Състояние "Инсталиран"

Нека разгледаме как RS-тригерът работи в това състояние, даден от стойностите R = 0 и S = 1. Тъй като входът 0 на елемента AND-NO Y е ниво 0, то Q̃ = 1 (AND-NO логика). От изхода Y сигналът Q̃ също се връща към елемента X (вход "А"). Тъй като S = A = 1, то Q = 0.

Ако е зададено R = 1, а вход S все още е 1, то на входовете Y имаме B = 0 и R = 1, а неговият изход е Q̃ = 1, т.е. не се е променил. Така че, ако S = 1, тогава RS схемата на спусъка „щраква” в „Инсталираното” състояние Q = 0 и Q̃ = 1, и промяната на сигнала R не го променя.

Състояние "Нулиране"

В това второ стабилно състояние, Q̃ = 0, и Q = 1, и то се определя от входовете R = 1 и S = 0. Тъй като елемент X има вход S = 0, неговият изход е Q = 1 (AND-NOT логика). Сигналът Q се връща обратно към елемента Y (вход "B"), и тъй като R = B = 1, тогава Q̃ = 0.

Ако S стане равен на 1, когато R = 1, тогава Q̃ остава равен на log 0, т.е. не се променя. Така че, при R = 1, задействащата верига отново е "заключена" в състояние "Нулиране" Q̃ = 0 и Q = 1, запаметено с всеки сигнал S.

Обобщаваме резултатите в таблицата

Можем да определим състоянието на Q и Q̃ сигналите, като използваме следната таблица на истината:

| състояние | S | R | Q | Q | описание |

| монтаж | 1 | 0 | 0 | 1 | Изход Q̃ = 1 |

| 1 | 1 | 0 | 1 | няма промяна | |

| нулиране | 0 | 1 | 1 | 0 | Изход Q̃ = 0 |

| 1 | 1 | 1 | 1 | няма промяна | |

| недопустим | 0 | 0 | 1 | 1 | състояние на грешка |

Може да се види, че когато S = R = 1, тогава Q и Q̃ могат да бъдат равни на 1 или 0 (но не едновременно!) В зависимост от нивата на S или R входовете преди настъпването на това състояние на изходите. Така, при условие S = R = 1, състоянието на изходите Q и Q̃ не може да се променя. Може да се промени само ако промените нивото от 1 на 0 на един от входовете.

Стойността S = R = 0 е нежелано или неприемливо състояние и трябва да се избягва. Състоянието S = R = 0 кара двата изхода Q и Q̃ да бъдат зададени на ниво 1, докато състоянието Q̃ винаги трябва да се връща към Q. Резултатът е, че спусъкът губи контрол над Q и Q̃, и ако сега два входа отиват в състояние 1, веригата става нестабилна и превключва на недефинирано състояние.

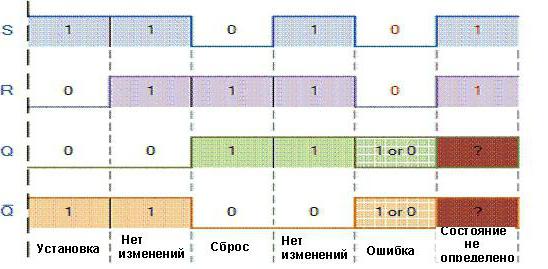

Диаграма на превключвателя на RS-Trigger

Това, което е казано в предишния раздел, е илюстрирано чрез следния модел на превключване.

Както може да се види, когато S = R = 0, възниква дисбаланс (несигурност) на състоянието на изходите. Това може да доведе до превключване на един от изходите по-бързо от другия, в резултат на което спусъка ще се превключи в едно или друго състояние, което може да не съвпадне с изискваното и данните ще бъдат повредени. Това нестабилно състояние обикновено се нарича метастабилно.

По този начин, подобен тригер-лост може да бъде прехвърлен в "инсталирано" състояние чрез подаване на 0 на неговия S-вход (ако има 1 на R-входа) и прехвърлен в състояние "Нулиране" чрез прилагане на 0 към R-входа (ако има 1 на S-вход). Тригерът влиза в недефинирано състояние (метастабилно), ако нивото 0 се прилага едновременно към двата му входа.

Превключването на състоянието на изходите става с малко закъснение, свързано с промяна на сигнала на един от входовете без използване на тактовия сигнал. Следователно горната схема е асинхронен RS-тригер.

Променете схемата за задействане

Както видяхме по-горе, основните елементи на IS-NOT на разглеждания RS-флип-флоп работят така, че когато той е зададен, Q̃ = 1 и Q = 0, и когато се нулира, Q̃ = 0 и Q = 1, въпреки че би било по-логично Q да има в първото състояние = 1, а във второто - Q = 0. В този случай се оказва също така, че промяната на състояния се случва, когато нивото на сигнала спадне от 1 на 0.

По този начин, за правилното функциониране на задействащата верига, неговите входни сигнали трябва да бъдат обърнати. След това преминаването на неговите състояния ще се случи при прилагане на положителни входни сигнали. За да направите това, добавете два допълнителни IS-NOT елемента към веригата, свързани като инвертори към S̃ и R̃ входовете, както е показано на фигурата по-долу. Тук входовете на елементите AND-NOT вече представляват обратни входни сигнали.

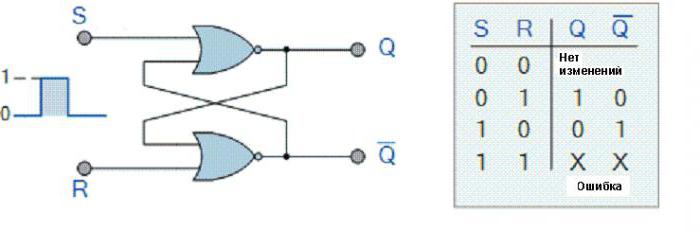

Точно както с използването на AND-NOT елементи, можете да изградите прост RS-тригер, използвайки два OR-NOT елемента, свързани по същия начин. Тя ще работи по същия начин, както схемата NAND, разгледана по-горе. В същото време, високото ниво на сигналите на входовете е активно и се получава неприемливо състояние, когато логическото ниво "1" е приложено към двата входа, както е показано в таблицата на истината на фигурата по-долу.

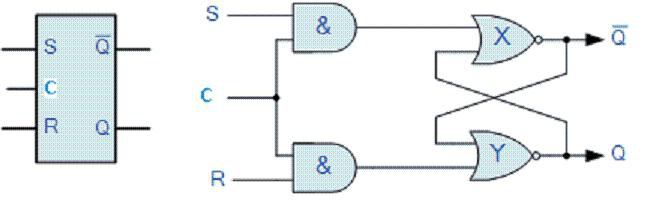

Как да синхронизирате спусъка

Понякога е желателно да има бистабилен тригер в последователни логически схеми, който променя своето състояние, когато са изпълнени определени условия, независимо от състоянието на S или R входовете. Такава схема може да бъде създадена чрез свързване на елемент с два входа И последователно с всеки вход на тригер. Комбинирайки двата входа на елементите, получаваме новия вход на спусъка. Добавянето му означава, че изходите Q и Q изход променят състоянието, когато сигналът по него е висок, и следователно може да се използва като часовник C-вход, както е показано на фигурата по-долу.

Когато сигналът на входа С е на ниво 0, изходите на двата А елемента също са на ниво 0 (логиката на елемента А), независимо от състоянието на двата входа S и R, и двата изхода Q и Q̃ са “заключени” в последното стабилно състояние. Когато сигналът при входа на С се промени на ниво 1, веригата реагира като нормален бистабилен тригер, като става прозрачен за настройване и нулиране на състояния.

Този допълнителен вход C също може да бъде свързан към изхода на генератора на тактовата честота и след това да образува синхронен RS тригер. По този начин, тази схема работи като стандартен бистабилен тригер "latch", но изходите се активират само когато ниво 1 се подава към C входа и се изключват, когато се появи логическо нулево ниво.

Тригерни регистри

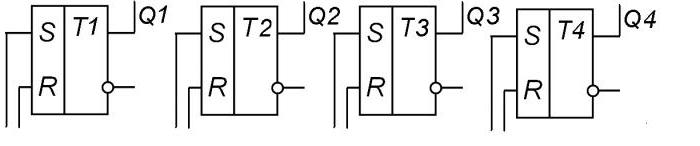

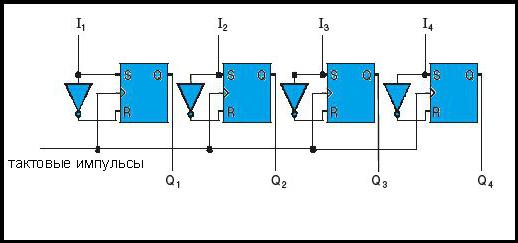

RS тригерът може да съхранява 1 бит цифрова информация. Ако е необходимо да се съхранят няколко бита, например цифрова двоична дума от няколко двоични битове (в микроконтролери, обикновено 8 или 16), тогава тригерите могат да бъдат свързани паралелно, образувайки регистри. Това са най-простите устройства за временно съхранение на набор от двоични цифрови цифри, в които всеки тригер запаметява стойността на една цифра (0 или 1. това е един бит). Така че 4-битовият регистър, показан по-долу на RS тригерите, съдържа четири отделни джапанки.

Всяко двоично число от (0000) 2 до (1111) 2 може да се съхрани в този регистър само чрез задаване или нулиране на съответния спусък. Да предположим, че първият тригер е настроен (Q1 = 1), вторият е нулиран (Q2 = 0), третият също е нулиран (Q3 = 0), а четвъртият е настроен (Q4 = 1). Тогава двоичното число, записано в регистъра, ще бъде (1001) 2.

В допълнение към паралелните регистри, предназначени за съхраняване на цифрови думи, се правят т. Нар. Преходни регистри на RS тригери, в които цифрите на цифровата дума последователно с пристигането на всеки тактов импулс се изместват наляво или надясно с един бит. Диаграма на такова устройство върху синхронните тригери е показана по-долу.

Тези регистри се използват в схеми за сериен интерфейс, когато цифровите думи, идващи от контролиращия контролер, се прехвърлят малко към комуникационната линия.